Member of the Royal Society of Chemistry 🏛️

Elected Member since 2025.

About the organization: UK’s professional body for chemical scientists with a worldwide community.

Semiconductor Advanced Packaging • Heterogenous Integration • Advanced Packaging Architecture

I am a semiconductor packaging leader specializing in advanced packaging and substrate technologies and advanced packaging architectures that enable next-generation CPUs, GPUs, and AI accelerators.

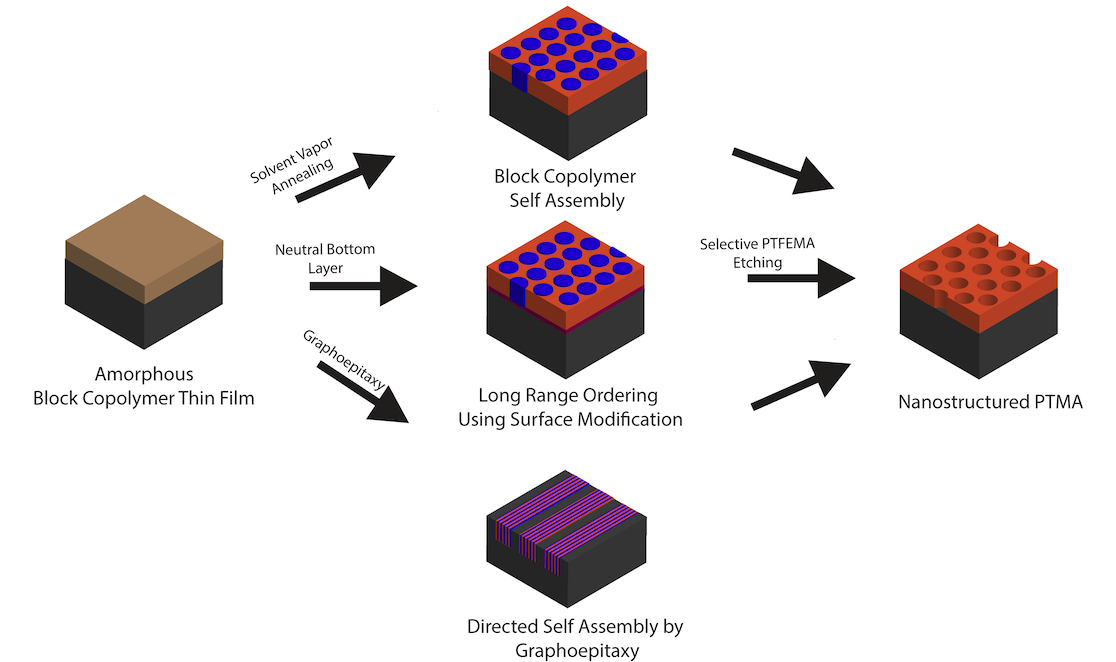

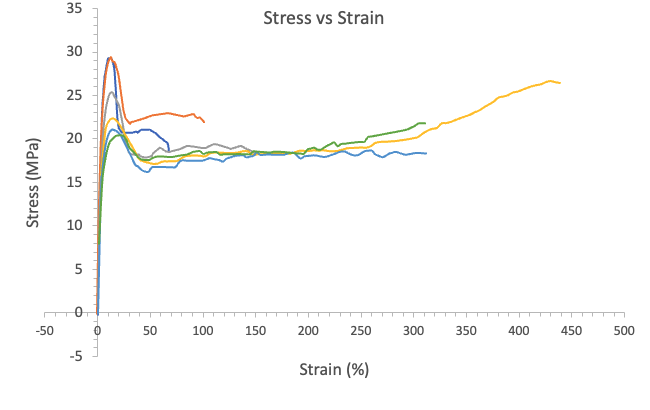

I’m a materials scientist and polymer technologist from Mumbai, India, currently living in Chandler, Arizona. I earned my bachelor’s degree in Polymer Engineering, focusing on polymer blending and structure–property relationships. My curiosity about applying polymers to the broader field of materials science led me to pursue a master’s in Materials Science at Cornell University, where I worked on block copolymer self-assembly of stable radical polymer blends. During my master’s, an internship at Intel introduced me to advanced semiconductor packaging, a field that quickly became my niche.At Intel, I have directed cross-functional teams spanning materials, design, and manufacturing to deliver substrate and package solutions that directly impact multi-billion-dollar product platforms. My work extends beyond execution: I influence technology roadmaps, evaluate ecosystem readiness, and ensure scalability from pathfinding through high-volume manufacturing.

Recently, I’ve led package architecture definition and developing technology strategies to align with Intel Foundry’s roadmap for 2.5D, 3D, and 3.5D architectures. In the past, I led pathfinding of key materials technologies that enabled Intel’s AI GPU packaging, including large form factor stiffener technology and EMIB-T materials technology. I’ve also pioneered new approaches, developing first-of-their-kind characterization techniques using AFM and XRD for advanced packaging. My work has resulted in 8 external publications and 7 internal publications in Intel’s packaging technology journal.

Recognized as an emerging industry leader by SEMI Americas' Semicon West 20 under 30, I actively contribute to the semiconductor packaging community through publications, peer-review, and cross-industry collaborations. My leadership philosophy combines technical depth with vision, enabling packaging strategies that accelerate the compute scaling while balancing cost, manufacturability, and performance.

Year: 2025 Awarded by SME SME spotlights the significant talent, contributions and innovation of young people impacting the future of manufacturing.

Year: 2024 Awarded by SEMI Americas For demonstrating outstanding leadership, practicing productive collaboration, exhibiting commitment to success and actively engaging in the community.

Elected Member since 2025. About the organization: UK’s professional body for chemical scientists with a worldwide community.

Committee Member since 2023. About the committee: Focuses on emerging, novel and unique material and packaging solutions. This committee places an international focus on the development, characterization, and commercial support for packaging, assembly, and test infrastructure for key applications areas such as, Fluidic Systems, Optical Systems, Automotive Systems, Military Systems, Medical Systems, Remotely Operated Systems, Telecommunications.

SME 30 Under 30 🏆

Semicon West 20 Under 30 🏆

Member of the Royal Society of Chemistry 🏛️

Member of the IEEE EPS Technical Committee on Emerging Technologies 🏛️

Research Interests

Benefits and Drivers for Advanced Packaging

What is a Semiconductor Package?

Why is Packaging Needed?

Standard vs Advanced Packaging